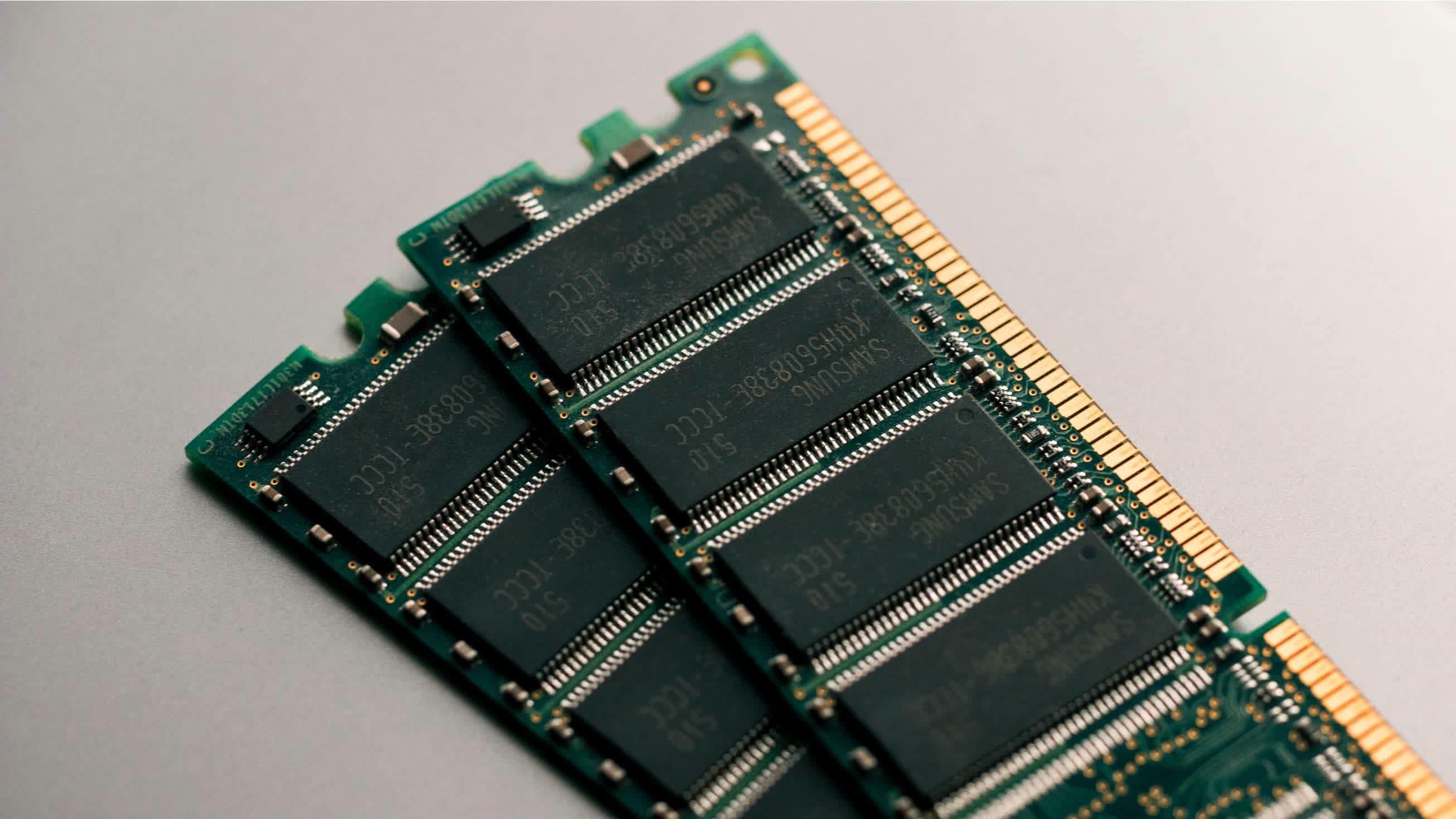

Samsung discusses next-generation DDR6 memory at Tech Day 2022

Forward-looking: The Intel 12th-gen Core Alder Lake launch officially brought DDR5 into the mainstream, giving users the option to select a legacy DDR4 or new DDR5-based platform. Unfortunately, ongoing cloth shortages and shipping delays take already made the new memory all but not-existent for most consumers. Despite the current platform'south availability and maturity challenges, Samsung has outlined futurity plans for the next generation of ultra-fast memory.

DDR5 is currently the new child on the block. It'south bigger, faster (in some ways, anyhow) and unfortunately very hard to find. Since the release of the new DDR standard, and now with Intel's 12th-gen Alder Lake CPUs, enthusiasts accept been eager to get their hands on any DDR5 memory kits to leverage the increase in retentivity speed and capacity. During this twelvemonth'southward Samsung's Tech Twenty-four hour period, the visitor tipped their paw and revealed plans for their side by side generation retention development, which is sure to capture the attention of speed freaks everywhere.

DDR5 doubled DDR4'south JEDEC standard speed, increasing from 3200 megatransfers per second (MT/due south) to 6400 MT/s. While not yet accepted equally a JEDEC standard, Samsung aims to again double the accepted standard speed with DDR6, increasing it to a whopping 12,800 MT/s, with theoretical overclock speeds equally loftier as 17,000 MT/s. The standard is currently in the early stages of evolution and scheduled for acceptance some time in 2024.

DDR6 isn't the just new memory standard on the horizon. Samsung also alluded to further development of the graphic-axial GDDR6, with a planned GDDR6+ standard reaching speeds of upward to 24,000 MT/due south.

Samsung is also hot on the heels of one of their main competitors, SK Hynix, who recently completed their first run of loftier-bandwidth memory iii (HBM3). Samsung plans to pursue HBM3 production as early on equally Q2 2022. HBM memory offers high performance computing (HPC) users a faster, more power efficient, merely college priced alternative to traditional GDDR retentiveness. The previous generation, HBM2, was used in AMD's Vega, Radeon 7, and Radeon Pro serial GPUs besides certain every bit Nvidia GPUs including the Titan Five and Quadro GP100.

Similar DDR5, DDR6 will increase the number of channels and banks on each module. These architectural differences, also as other factors such every bit memory timings, latency, ability direction, and fault correction code (ECC) capabilities, are all factors contributing to Samsung'southward power to continue pushing the boundaries of memory speed and reliability.

Source: https://www.techspot.com/news/92315-samsung-discusses-next-generation-ddr6-memory-tech-day.html

Posted by: begayeelbectern.blogspot.com

0 Response to "Samsung discusses next-generation DDR6 memory at Tech Day 2022"

Post a Comment